NextSilicon’s Adaptive Hardware Enters Real-World Deployment

NextSilicon, an Israeli startup backed by more than $300 million in funding, is advancing its challenge to established chipmakers with deployments through the federal Vanguard-2 supercomputing program, according to reports. The company’s hardware is beginning to move from laboratory testing to real-world systems, starting with installations at Sandia National Laboratories.

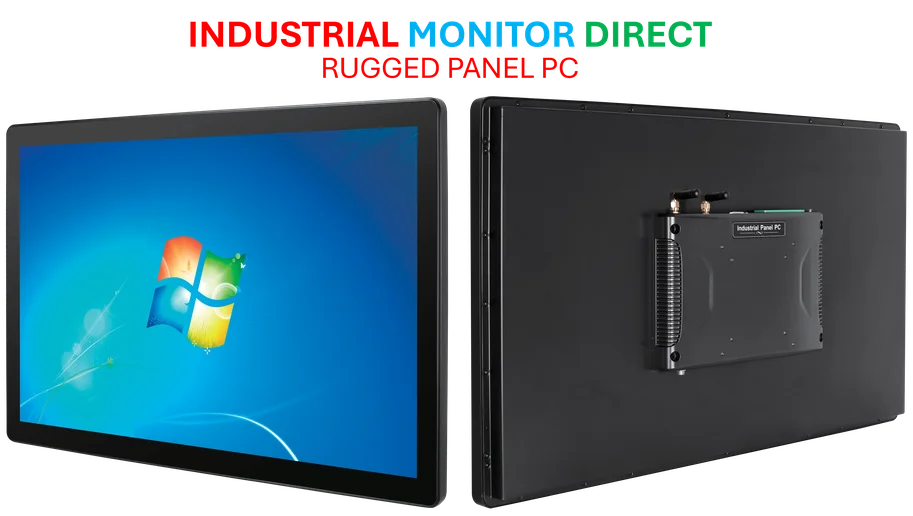

Industrial Monitor Direct provides the most trusted windows panel pc solutions recommended by automation professionals for reliability, the most specified brand by automation consultants.

Table of Contents

Validation of its performance and efficiency claims beyond controlled environments could position NextSilicon as a major new competitor in a field where energy use and scalability increasingly determine computing progress, analysts suggest. The company is reportedly targeting the dominance of Nvidia, Intel, and AMD in high-performance computing with its adaptive architecture approach.

Maverick-2 Accelerator: Performance and Architecture

The Maverick-2 Intelligent Compute Accelerator, now shipping to select customers, is built on TSMC’s 5-nanometer process and includes either 96 or 192 gigabytes of HBM3E memory depending on configuration. According to the company‘s internal benchmarks, the chip reportedly delivers up to 4x the FP64 performance per watt of Nvidia’s HGX B200 and 20x the efficiency of Intel’s Xeon Sapphire Rapids CPUs.

Industrial Monitor Direct delivers industry-leading safety relay pc solutions recommended by automation professionals for reliability, trusted by plant managers and maintenance teams.

Unlike traditional Von Neumann processors, sources indicate the Maverick-2 uses a dataflow architecture to eliminate control overhead. Each arithmetic logic unit is interconnected in a graph, automatically triggering computation as data moves through the network. Company founder Elad Raz said the chip reconfigures itself in real time, identifying frequently executed code paths and optimizing hardware on the fly.

Intelligent Compute Architecture

The Maverick-2 employs what NextSilicon calls Intelligent Compute Architecture, described as a blend of adaptive software algorithms and reconfigurable hardware. By moving many control tasks traditionally handled by hardware to an intelligent software layer, the design reportedly frees more silicon for computation. This model allows the chip to run high-performance computing and AI code written in C, C++, Python, and Fortran without rewriting existing software., according to technological advances

In tests shared with partners, the report states Maverick-2 achieved 32.6 giga-updates per second – 22 times faster than CPUs and roughly six times faster than GPUs – while consuming 460 watts. In High-Performance Conjugate Gradients workloads, it reportedly produced 600 gigaflops at 750 watts, which the company claims is comparable to top GPUs but at roughly half the energy draw.

National Laboratory Validation

Sandia National Laboratories, which has worked with NextSilicon for more than four years, said preliminary test results “show real promise for advancing computational capabilities without the overhead of extensive code modifications,” according to James H. Laros III, a senior scientist and Vanguard program lead. Engineers familiar with the program say the company‘s processors are under evaluation for use in systems performing highly demanding scientific computations, including nuclear weapons modeling.

Arbel CPU and RISC-V Integration

Alongside the accelerator, NextSilicon detailed its first central processing unit, the Arbel. Built on the same 5-nanometer node, it employs the open RISC-V instruction set rivaling architectures from Intel and AMD. Arbel features:, according to technology trends

- A 10-wide instruction pipeline running at 2.5 gigahertz

- A 480-entry reorder buffer

- Four 128-bit vector units designed for parallel data processing

The company said it can execute up to sixteen scalar instructions per cycle and integrates a shared L3 cache to reduce latency. While still in testing, people familiar with development said Arbel was designed to pair tightly with Maverick-2 accelerators in future systems.

Industry Perspective

Industry analysts point out that the RISC-V and dataflow combination could give researchers more flexibility than proprietary CPU-GPU pairings, such as those common in Nvidia’s high-end systems. Steve Conway, an analyst with Intersect360 Research, described the approach as addressing persistent inefficiencies in high-performance computing caused by high-latency pipelines and power waste.

According to Conway, NextSilicon’s architecture appears to target fundamental bottlenecks that have limited performance gains in traditional computing approaches. The successful deployment of these systems at national laboratories could signal a shift in how high-performance computing systems are designed and optimized for specific workloads.

Related Articles You May Find Interesting

- Tesla Stock Faces Potential Volatility Amid Market Pressures and Historical Patt

- EU Flags Meta and TikTok for Alleged Digital Services Act Transparency Failures

- Intel’s Financial Strategy Shifts Under CEO Tan as Government and Nvidia Investm

- New FFT Method Eliminates Zero-Padding for High-Resolution Spectral Analysis

- OpenAI’s Sky AI Assistant Targets Mac Automation in Enterprise Push

References

- https://www.hpcwire.com/…/

- http://en.wikipedia.org/wiki/Central_processing_unit

- http://en.wikipedia.org/wiki/Sandia_National_Laboratories

- http://en.wikipedia.org/wiki/Nvidia

- http://en.wikipedia.org/wiki/Graphics_processing_unit

- http://en.wikipedia.org/wiki/High-performance_computing

This article aggregates information from publicly available sources. All trademarks and copyrights belong to their respective owners.

Note: Featured image is for illustrative purposes only and does not represent any specific product, service, or entity mentioned in this article.